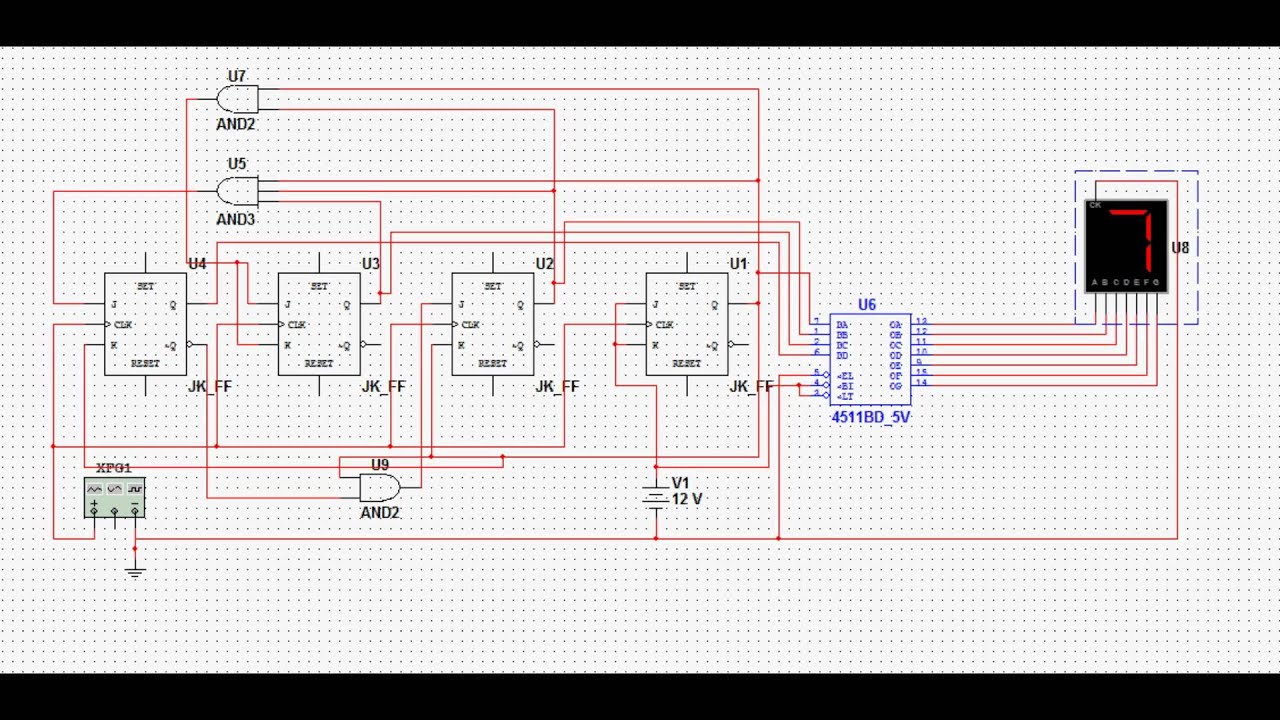

However, it is probably unfamiliar to many, and is certainly less familiar than other implementations of T flip-flops, such as the master-slave implementation, or the 6 nand gate implementation shown in another answer. In this answer, such a circuit will be shown. Such asynchronous finite state machines may be implemented in a number of ways, but one way to do so is with a sum-of-products combinatorial circuit with some of the outputs fed back as inputs.

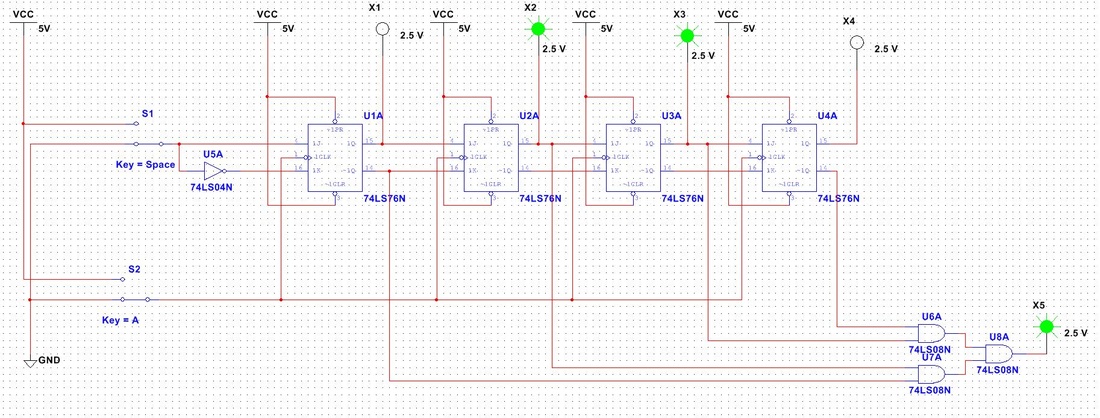

An asynchronous finite state machine without hazards (or race conditions) or with hazards which are "covered" (and hence not active) will perform properly if there is at any time only one signal which is changing, and which does not receive new inputs until the circuit has reached a stable state. As such, the circuit will only work properly if the delays within the circuit are properly controlled.Īn asynchronous finite state machine with hazards (or race conditions) will, in general, work properly only if delays within the circuit are properly controlled. The circuit in the original question contains 1 or more hazards or race conditions. There are 4 stable states and 12 states that are transistional between stable states in normal operation. I will provide this information, but not as a diagram. For example, the OPs circuit, shows up all over the place labeled as a T flip-flop despite the fact that it has problems described in other answers.) However, I am offering the above information as an alternative point of view to that of the commenter.Įdit2: A commenter has asked for a state diagram for the circuit. (There is certainly a lot of misinformation about flip-flops on the interwebs. I don't claim that this is necessarily an authoritative refutation of the claim that a T flip-flop must have separate T and clock inputs. It can be made from a J-K flip-flop by tying both of its inputs high. It is useful for constructing binary counters, frequency dividers, and general binary addition devices. The T or "toggle" flip-flop changes its output on each clock edge, giving an output which is half the frequency of the signal to the T input. However, when I google "T flip-flop", the very first hit that comes up for me is this which states: Someone has commented that this circuit is not a T flip-flop because the circuit depends upon the clock alone, and does not have separate T and clock inputs. Simulate this circuit – Schematic created using CircuitLab

The circuit below simulates fine in CircuitLab. To implement an edge triggered T Flip-Flop that does not rely on gate delay timing, requires, I believe, a minimum of 6 Nand gates.

0 kommentar(er)

0 kommentar(er)